名前の由来は、Metal(金属)、Oxide(酸化物)、Semiconductor(半導体)Field Effect (電界効果)、Transistor(トランジスタ)の略です。

モーター駆動などのスイッチング素子またはリレー駆動素子として利用されることが多いです。特に大電流を高速にスイッチするのに適しています。

バイポーラトランジスタは電流駆動でしたが、MOS FETは電圧駆動であるため原理的には駆動損失(電力ロス)が発生しないことが特徴です。。

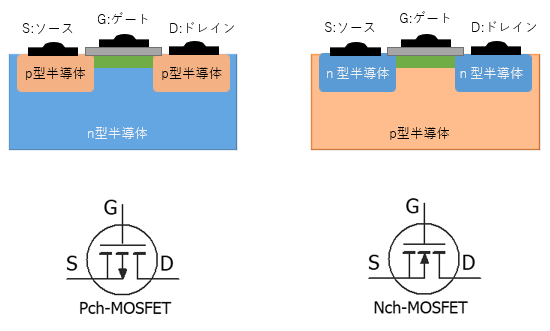

バイポーラトランジスタと同じく3本の端子が出ていますが、名称が異なりゲート(G)、ドレイン(D)、ソース(S)と呼ばれている端子が出ています。バイポーラトランジスタには構造によってNPN型とPNP型がありましたが、MOS FETも構造によりNchとPchに分けられます。

MOS FETの構成

MOSFETもp形半導体とn形半導体を組み合わせてできたものです。組み合わせ方によっていくつかのMOS FETが。

p型半導体、n型半導体などの半導体の基礎についての詳しい内容・説明などは「半導体とは」に記載していますのでこちらを参考にしてください。

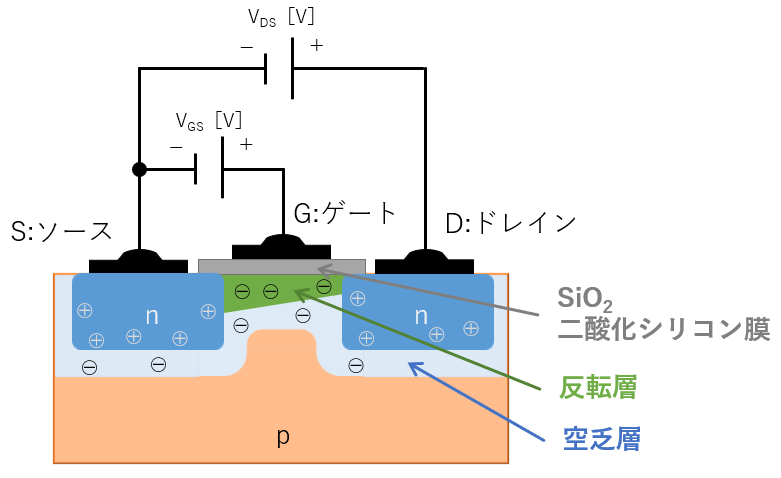

構成としては、ゲート端子などの黒く塗りつぶされたところが「金属」で、ゲート端子と半導体の間のグレー部分が「シリコン酸化物」、そして「半導体」と3枚がサンドイッチのように貼り合わされています。

MOS FETの動作原理

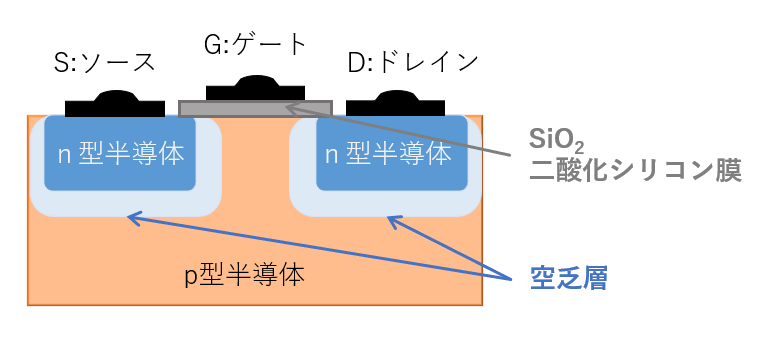

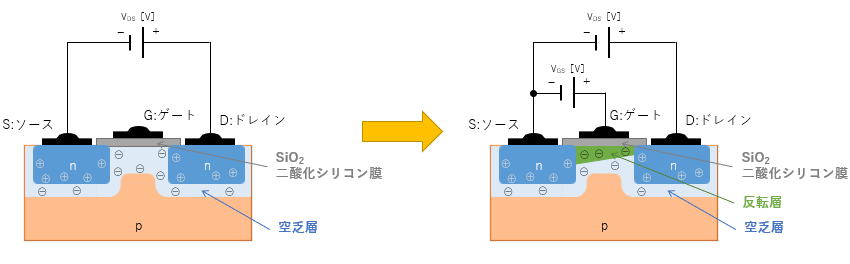

どの端子にも電圧を印加していない状態です。

半導体部にはp型半導体の中に、n型半導体が2個層を成しています。バイポーラトランジスタで言えば、npn形と言えますが、真ん中のp型半導体が薄くなっていません。

この状態では、n型半導体とp型半導体の境界面では、自由電子と正孔がpn結合を起こしキャリアが存在しない部分、つま「空乏層」が存在することになります。

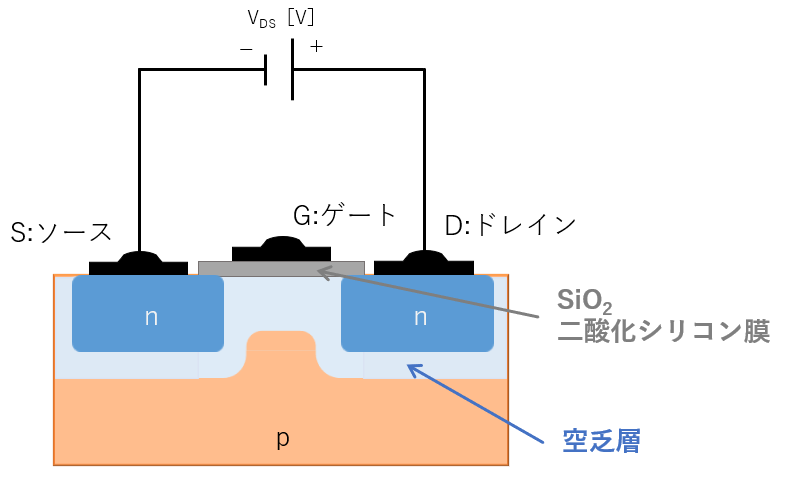

この状態で、ドレイン-ソース間に電圧(VDS)を印加してみます。

半導体部分は、npn構造です。ダイオードのところでも話しましたが、電流はp→nへ流れますので、この構造では外向きにダイオード結合されている形となります。よって、電圧を印加しても電流は流れなく、絶縁状態ですのでドレイン電流IDはゼロです。

さらに、ダイオードが逆方向電圧に印加されていますので、空乏層の領域は拡がっています。

この状態で、ゲート電圧(VGS)を印加してみます。

ゲート端子とp型半導体の間に、シリコン酸化物(SiO2)という絶縁物が挟まっています。いま、この構造は「コンデンサ」の構造と同じで、電極が酸化膜を挟んでいるため十分なコンデンサになります。

よって、ゲート端子がプラスになるように電圧を印加すると、電極間の誘電体は誘電体の誘電分極※による作用により、ゲート端子には「正の電荷」が、そして、半導体表面には「負の電荷」が集められます。(※誘電分極はコンデンサに記載しています。)

p型半導体のゲート端子に近いところに、ゲート部のコンデンサ効果により、自由電子が集められ、p型半導体なのに「自由電子」が多いという、いわゆる“反転層”が存在することになります。

空乏層もマイナスの電荷を帯びていますが、pn結合によりキャリア(自由電子)が消滅しているので電流を流すことができません。しかし、この反転層のおかげで、自由に動くことのできる電子が集められドレイン-ソース間に電流を流すことができるようになります。

MOS FETの4つの領域

MOS FETの動作原理のところで見てきましたが、この素子には4つ領域が存在します。それぞれの領域については以下の通りとなります。

| 領域 | 内容 |

| 動作しない領域 | ゲート電圧がある値以下の場合を言います。反転層を作り出すことのできない電圧領域となります。 |

| 線形領域 | ドレイン電圧を印加しさらにゲート電圧がある程度印加すると、ドレイン電流が流れ始めます。この領域では、ドレイン-ソース間がある抵抗値(オン抵抗:RON)を持って、ドレイン電圧とドレイン電流が比例の関係にあります。 |

| 飽和領域 | ドレイン電圧を大きくしていくと、ある電圧に達すると電流が増加しない点があります。いわゆる電流が飽和してしまった状態のことです。 |

| 降伏領域 | さらにドレイン電圧を大きくしていくと、一気に電流が流れる点があり、この領域はMOSFETが破壊するモードに入っていくので、使用禁止の領域です。 |

トランジスタとMOS FETとの比較

これまでの内容をまとめて簡単にバイポーラトランジスタとMOS FETとの比較したものを表にしました。

| バイポーラ トランジスタ |

MOS FET | |

| 駆動 | 電流(ベース電流) | 電圧(ゲート電圧) |

| 入力インピーダンス | 低い | 高い |

| スイッチングスピード | 遅い | 早い |

| 電力損失 | 大きい | 少ない |

FETの名前と外形

FETの名前は、バイポーラトランジスタと同様一般的に「2S」から始まります。例えば、代表的な型番の「2SJXXXX」と記載されます。ただしJFET(ジャンクションFET)とMOSFETとの区別はありません。

| 型名 | 意味 |

| 2 | 接合面の数。 |

| S | Semiconductorの「S」 |

| J | J・・・Pch電界効果トランジスタ K・・・Nch電界効果トランジスタ |

| XXXX | 日本電子機械工業会(EIJA)への登録番号 |

FETの許容損失PDとオン抵抗RDS(ON)

オン抵抗RDS(ON)

ゲートに電圧を加え、MOS FETを動作(オン)させた時のドレインとソース間の抵抗値のことをオン抵抗RDS(ON) といいます。値が小さいほど、動作時のロス(電力損失)が少なくなります。

FETの許容損失PD

バイポーラトランジスタの場合、消費する電力はコレクタ飽和電圧 VCE(sat) とコレクタ電流ICの積で表します。

コレクタ損失PC[W]=コレクタ飽和電圧 VCE(sat)[V] ×コレクタ電流 IC[A]

それに対し、MOS FETの消費電力はドレイン・ソース間のオン抵抗 RDS(ON) を使います。MOS FETが消費する電力PDはMOS FET自身が持つオン抵抗にドレイン電流IDの2乗をかけ算したもので表します。

電力PD[W]=オン抵抗 RDS(ON)[Ω]×ドレイン電流 ID2[A]

この電力は熱となり放出されます。